Throughout the opening keynote at Intel’s Development occasion in San Jose, Ceo Pat Gelsinger revealed a rating of information about the upcoming Meteor Lake customer platform. Intel’s Meteor Lake marks the start of a brand-new age for the chipmaker, as they move far from the disorderly Intel 7 node and enter into a rollout of their Foveros 3D product packaging with EUV lithography for their upcoming customer mobile platform. Meteor Lake utilizes a tiled, disaggregated chiplet architecture for its client-centric processors for the very first time, altering the very nature of Intel’s customer chips moving forward. And, according to Intel, all of these modifications have actually enabled them to bring some considerable developments to the mobile market.

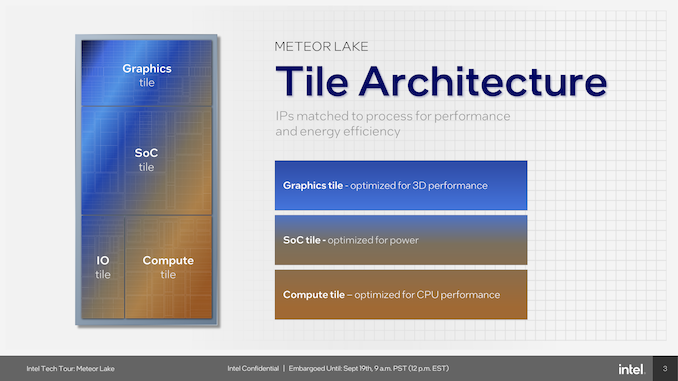

Intel’s very first chiplet-based customer CPU separates the typical functions of a contemporary CPU into 4 private tiles: calculate, graphics, SoC, and an I/O tile. Within the makeup of the calculate tile is a brand-new set of cores, a P-core called Redwood Cove and a brand-new E-core called Crestmont. Both these cores assure IPC gains over their previous equivalents, however maybe the most intriguing addition is a brand-new kind of E-core ingrained straight into the SoC tile, which Intel calls ‘Low Power Island.’ These brand-new LP E-cores are developed with the concept that light work and procedures can be removed the more power-hungry calculate tile and unloaded onto a more effective and lower-powered tile completely. Other significant additions consist of a first-for-Intel Neural Processing System (NPU), which sits within the SoC tile and is developed to bring on-chip AI abilities for work and inferencing, leading the way for the future.

With Meteor Lake, Intel is intending to put themselves in a more competitive position within the mobile market, with noteworthy enhancements to calculate core hierarchy, Intel’s Xe-LPG Arc-based graphics tile aiming to reinforce integrated graphics abilities, and an NPU that includes different AI benefits. Meteor Lake likewise sets the scene for Intel and modular disaggregation, with Foveros 3D product packaging set to end up being an essential of Intel’s processor roadmap for the future, with the Intel 4 procedure making its launching and functioning as a stepping stone to what will end up being Intel’s next essential node throughout its fabs, Intel 3.

Intel Meteor Lake: Intel 4 Utilizing Foveros 3D Product Packaging

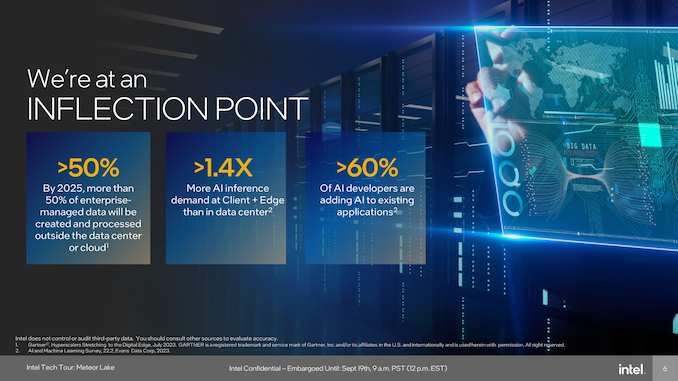

Intel’s Meteor Lake architecture is not simply another model in the long line of processor developments; according to the business it’s an advanced leap forward. Eloquently put by the executive VP and GM of Intel’s Customer Computing Group (CCG), Michelle Johnston Holhaus, at Intel’s Tech Trip 2023 in Penang, Malaysia, she said that Intel had actually reached an inflection point in their customer roadmap. Revealing more information about Meteor Lake at the Intel Innovation Trip in Malaysia, the architecture is an improvement from its present customer processors concerning efficiency as we advance through Intel’s ‘5 nodes in 4 years’ roadmap.

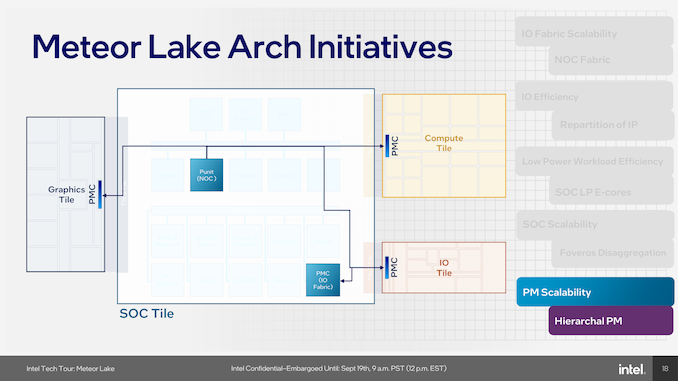

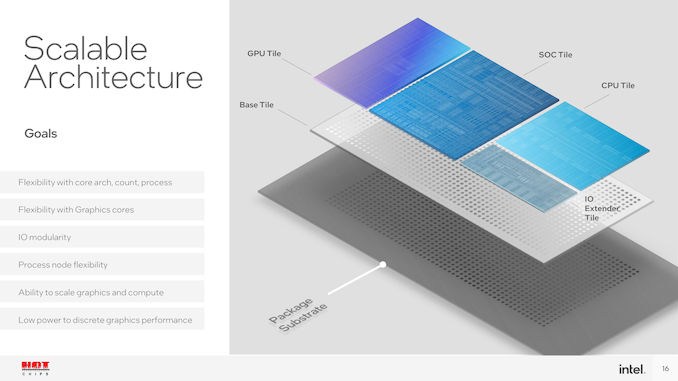

Meteor Lake is built on Intel’s disaggregated architecture pressed through by Foveros product packaging. This is developed to enhance both efficiency and energy performance. The architecture itself includes 4 special and unique tiles linked by means of Intel’s Foveros 3D product packaging innovation. This consists of the calculate tile, which is developed on Intel 4, while the graphics tile is developed on TSMC’s N5 node. The other 2 tiles Intel carries out within Meteor Lake are the SoC tile which functions as the main center through the ingrained NOC. This is the very first time Intel has actually utilized a Network-on-Chip (NOC) on their customer processors, which is a streamlined method to the NOC on their existing Agilex FPGAs. While on Agilex, the NOC is embellished into various NoC targets and switches within the base of the NoC, on Meteor Lake, it straight links to the I/O material through the IoC, which then enters into the I/O material. The NOC itself is straight linked to the graphics tile, calculate tile, and other parts within the SoC.

This modular method enables a ground-up and scalable power management architecture that supports disaggregation, making it possible for each tile to work individually. This disaggregated style focuses on efficiency by negating bandwidth bottlenecking through things like the I/O on a monolithic style and targets boosted power performance. Maybe the most noteworthy component of disaggregation is that Intel can choose particular silicon procedures for each tile and isn’t restricted to one procedure node. On top of the power performance and plan location advantages of a tiled architecture, it is more affordable for Intel to produce CPUs with less masks through EUV, however it permits Intel to scale out brand-new IP into future items while keeping the very same base, which is another cost-saving aspect (for Intel).

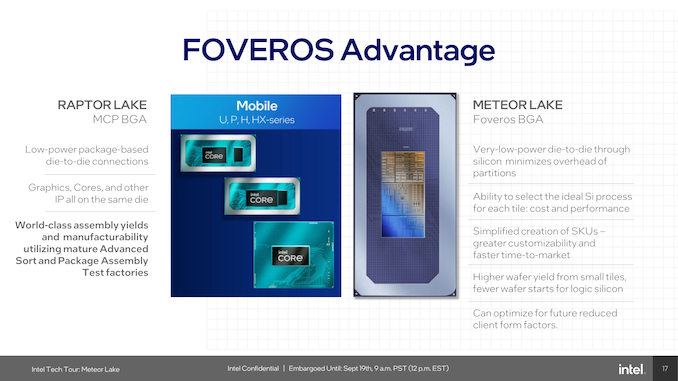

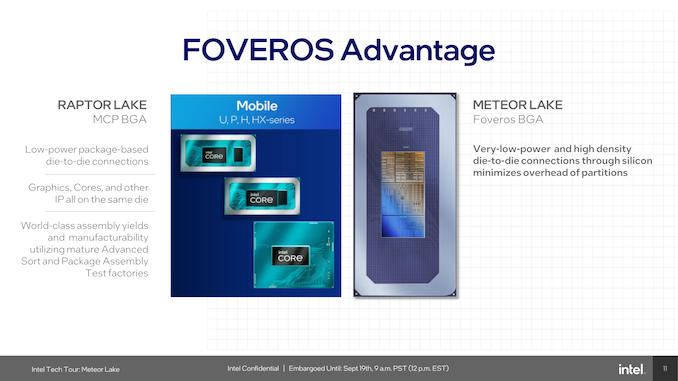

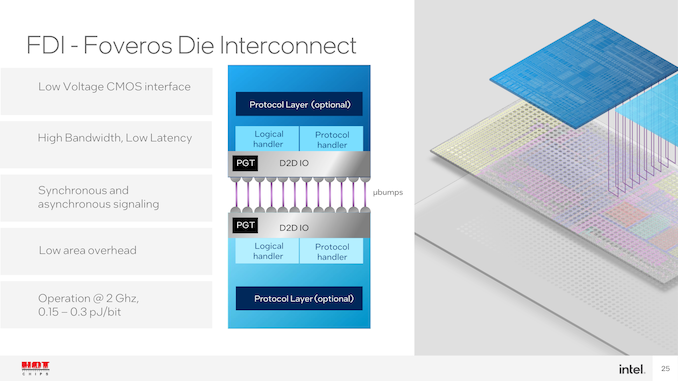

Compared to mobile Raptor Lake, which was done utilizing Multi-Chip Product packaging (MCP), Meteor Lake utilizes Foveros BGA product packaging and provides low-power die-to-die interconnects, which Intel validated has a little power charge of in between 0.15 and 0.3 picojoules (pJ) interacting from tile to tile. A few of the benefits of Foveros consist of much better customizability through tiling, which permits Intel to produce chips and carry out particular tiles and IP depending upon the grade of the chip, and so on, low power with more I/O, or high-end tiles with all the current gizmos and devices. With the Intel 7 node not being as practical as they would have hoped, Intel assures greater wafer yield on Intel 4, which utilizes less wafer area for logic-based silicon.

Power management is done utilizing a scalable power management system that supports the independent performance of each tile. Coordination in between numerous power management controllers (PMC) and system software application is developed to be enhanced for different work. Intel’s Meteor Lake architecture likewise presents a brand-new scalable material to enhance energy performance and extend bandwidth in locations that have actually been formerly bottlenecked, such as I/O.

Touching more on the power controllers within the Meteor Lake architecture, Intel has actually incorporated independent Power Management Controllers within each of the tiles. As part of the disaggregation of utilizing Foveros, each tile requires to be individually power handled, and utilizing PMCs on the NOC, the I/O material, in addition to each tile permits power management to be agnostic depending upon the variety of the cores on each plan.

Meteor Lake itself represents a significant architectural shift, not simply a simple incremental upgrade, as it represents the most considerable architectural change in customer processors in 4 years. This is since it’s the very first customer processor to be used chiplets rather of a monolithic style. The architecture is developed to be the foundation of Intel’s method to press PC development for the next years. Taking a look at a few of the finer information of Intel’s Meteor Lake architecture, it utilizes Intel’s Foveros product packaging innovation, which utilizes 3D chip stacking to take on the mistakes of standard 2D chip designs.

As we can see from the above disclosure from Intel at Hot Chips 2023, the leading and bottom layers have bumps for adjoining each pass away together. Utilizing the Foveros FDI product packaging provides a low-voltage complementary metal oxide semiconductor (CMOS) user interface, which indicates the power circuitry can be kept up lower voltages and, therefore, with a lower power envelope. Another advantage of FDI is both concurrent and asynchronous signaling, which indicates signal transmission can deal with totally duplexed information blocks.

Building a Meteor Lake SoC consists of a bundle substrate, which is the structure for the base tile to sit onto, which utilizes the Foveros Pass away Interconnect (FDI). The base tile has a 36µm die to pass away pitch with metal layering and a 0.15 to 0.3 pJ operating power at 2 GHz; this might vary or differ depending upon voltages, amps, and frequency. As it’s a base tile that isn’t an active chiplet itself, its only function is to function as a base for all of the different reasoning, and metal layers for the chiplets to be positioned upon.

The makeup of Intel’s Meteor Lake architecture utilizes 4 unique tiles to develop a Meteor Lake CPU. This consists of a Compute, SoC, GPU, and an I/O tile, all with unique usages, abilities, and versatility in regard to IP. Power management likewise gets a revamp. With disaggregation through Intel’s Foveros product packaging innovation, each tile in Meteor Lake needs its own power management. Intel’s option is a hierarchical power management system that utilizes Power Management Controllers on the NoC, IO material, and each private tile.

Over the next couple of pages, we’ll provide an insight into each of the 4 tiles, what each tile gives the table, and more about the different innovations driving development through Meteor Lake.